Vías microciegas y enterradas para circuitos ultrafinos

Vías microciegas y enterradas para circuitos ultrafinos

Maximiza el ahorro de espacio y la densidad funcional

Maximiza el ahorro de espacio y la densidad funcional

Permite una mejor integridad de la señal con interconexiones más cortas

Permite una mejor integridad de la señal con interconexiones más cortas

Admite un mayor número de capas en estructuras de placas más delgadas y livianas

Admite un mayor número de capas en estructuras de placas más delgadas y livianas

Se utiliza en teléfonos inteligentes, tabletas y dispositivos electrónicos portátiles.

Se utiliza en teléfonos inteligentes, tabletas y dispositivos electrónicos portátiles.

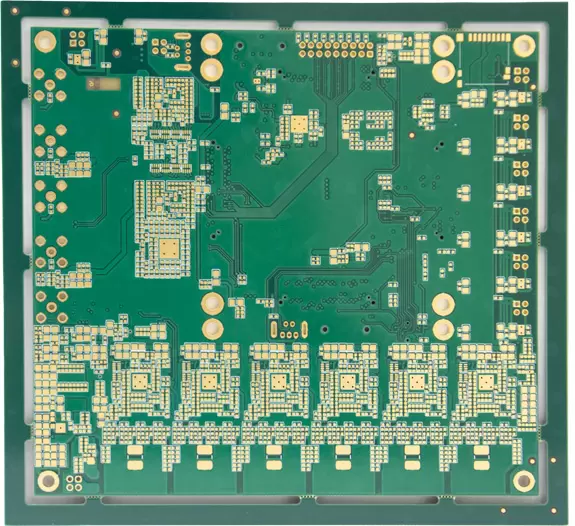

| Característica | Especificaciones técnicas |

| Número de capas | 4 – 24 capas estándar, 40 capas avanzadas, 60 capas prototipo |

| Construcciones HDI | 3+N+3, 4+N+4, cualquier capa en I+D |

| Espesor de PCB | 0,40 mm – 6,0 mm |

| Pesas de cobre (terminadas) | 0.5 oz – 6 oz |

| Materiales | FR4 de alto rendimiento, FR4 sin halógenos, Rogers |

| Dimensiones máximas | 546 mm x 662 mm |

| Pista y espacio mínimos | 0,075 mm / 0,075 mm |

| Taladro mecánico mínimo | 0,15 milímetros |

| Acabados superficiales disponibles | HASL (SnPb), LF HASL (SnNiCu), OSP, ENIG, Estaño de inmersión, Plata de inmersión, Oro electrolítico, Dedos de oro |

| Taladro láser mínimo | 0,10 mm estándar, 0,075 mm de avance |

| Procesos especiales | Vías ciegas/enterradas, vías en plataforma, perforación posterior, placas laterales, agujeros avellanados |

![]()

Soporte de ingeniería

![]()

Servicios de creación de prototipos

![]()

Entrega rápida

![]()

Transición fluida a la producción en masa

¿Cómo selecciono materiales para HDI?

¿Cómo selecciono materiales para HDI?  ¿Por qué debería recurrir a las PCB HDI?

¿Por qué debería recurrir a las PCB HDI?  ¿Cuál es la precisión del taladro láser?

¿Cuál es la precisión del taladro láser?  ¿Cómo los PCB de HDI mantienen bajos mis costos?

¿Cómo los PCB de HDI mantienen bajos mis costos?  ¿Qué es una PCB HDI?

¿Qué es una PCB HDI?

Atención al cliente